金屬材料在裝修設施與施工中的應用——以江陰市華士晟義金屬制品廠為例

在現代裝修設施與施工中,金屬材料因其優異的性能和廣泛的應用場景,已成為不可或缺的重要元素。江陰市華士晟義金屬制品廠作為專業從事金屬材料生產的企業,其產品在裝修領域發揮著關鍵作用。本文將從金屬材料的特性、在裝修設施中的具體應用、施工要點以及華士晟義金屬制品廠的優勢等方面展開闡述。

金屬材料具有高強度、耐腐蝕、易加工等特點,使其在裝修設施中備受青睞。以江陰市華士晟義金屬制品廠為例,其生產的金屬材料包括不銹鋼、鋁合金、鋼材等,這些材料不僅外觀美觀,還能滿足不同裝修風格的需求。例如,不銹鋼常用于廚衛設施,鋁合金多用于門窗框架,而鋼材則廣泛用于建筑結構和裝飾構件。

在裝修設施中,金屬材料的應用范圍極其廣泛。華士晟義金屬制品廠提供的金屬材料可用于室內外裝飾、結構支撐、防護設施等多個方面。具體來說:

- 室內裝修:金屬扶手、樓梯護欄、吊頂龍骨等,不僅增強空間美感,還提升安全性。

- 建筑結構:金屬梁柱和框架在大型裝修項目中提供穩定的支撐,尤其在商業空間和工業廠房中應用廣泛。

- 外立面與景觀:金屬幕墻、圍欄和雕塑等,為建筑增添現代感和耐久性。

施工過程中,金屬材料的應用需注意關鍵要點。華士晟義金屬制品廠強調,施工前應根據設計圖紙精確切割和加工金屬材料,確保尺寸匹配。安裝時需使用專業工具和連接件,如焊接、螺栓固定等,以保證結構的牢固性。金屬表面處理(如噴漆、電鍍)能有效防止銹蝕,延長使用壽命。施工團隊還需遵循安全規范,避免材料變形或損壞。

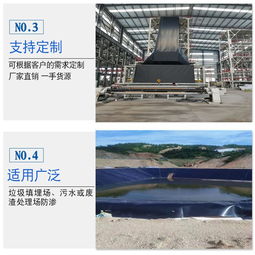

江陰市華士晟義金屬制品廠在金屬材料領域具備顯著優勢。該廠擁有先進的生產設備和嚴格的質量控制體系,確保產品符合國家標準和環保要求。其金屬材料不僅強度高、耐候性好,還可根據客戶需求定制規格和表面處理,滿足個性化裝修項目。工廠還提供技術支持和售后服務,協助施工方優化材料使用,提升整體裝修效率。

金屬材料在裝修設施與施工中扮演著重要角色,江陰市華士晟義金屬制品廠以其優質產品和專業服務,為行業提供了可靠支持。隨著綠色建筑和智能裝修的發展,金屬材料的創新應用將進一步推動裝修行業的進步。

如若轉載,請注明出處:http://www.oifrewe.cn/product/44.html

更新時間:2026-04-24 14:49:25